: m+ O( q9 g$ y7 S. W% _% F3 J- d6 e6 S* l) k" ]; U- b A

近日,由韩国蔚山科技大学Kim Kyung-rok教授领导的研究小组成功研发了世界上第一个大尺寸晶圆上的三进制半导体设计,这对未来开发低功耗和高效能的微芯片有重要的意义。此外,此项研究对促进人工智能,自动驾驶,物联网和机器人技术的发展有积极意义。 % h1 y; m: o ~2 w0 f

r; T0 G" Y l' b) b$ L

; w F& ~; K3 \* h u. V

3 [) ^4 ]5 x4 K; Y- {0 VKim团队介绍说,最新的研究表明,目前芯片的制造工艺有机会实现三进制半导体商业化生产,这将引起半导体产业的革命。

% G9 K# _$ X, ?6 G: Z

! T, M3 B9 j/ o( C* t) b* |2 s6 I# C8 ]4 z/ w

三星电子自2017年9月起通过2013年推出的价值1.5万亿韩元(12.7亿美元)的研究补助计划为该研究提供支持。

6 ~' b0 C3 q/ h$ D, {

& x0 n( k/ D) b6 j; i! s# f6 S6 N9 c# @' H7 |

# N- S$ I/ Z: Y& W7 Q5 B6 m1 D& m4 u

单位面积可减少37%器件数量!摩尔定律即将到达极限时,三进制半导体给产业带来曙光 $ }6 X* R( J9 X" {. B# g2 j

0 T- \8 ?: v4 e P1 h z

自从20世纪60年代后期,硅基金属氧化物半导体的场效应晶体管(MOSFET)发明以来,已经按照摩尔定律发展了半个世纪,计算机系统已经得到飞速的发展。但是在2000年以来,硅基半导体的几何尺寸已经逼近了物理极限,但是通过引入更高性能材料、改善器件结构,已经实现了10nm制程工艺,即每平方毫米1亿个晶体管的器件密度。4 N- h7 {) ~9 Q0 A# R/ O- ?, P

% _) U! Q, X# X+ \

1 L3 c% D1 `! d$ Y

. Z: ]1 v! I- L4 ?! Y0 [

此外,三星和台积电两大半导体厂商通过导入13.5nm极紫外(euv)光刻技术,实现了7nm技术的量产,目前更是在积极推动5nm和3nm工艺的研发。然而,在这之后,仅仅通过工艺的优化,半导体设备将很难进一步缩小尺寸,研发人员也在积极寻找替代硅基半导体的材料。& J2 b8 r) h* H$ Z- E# R8 Y1 L

" M& w) u- l9 H0 e. C: V/ b0 m! g7 p9 e

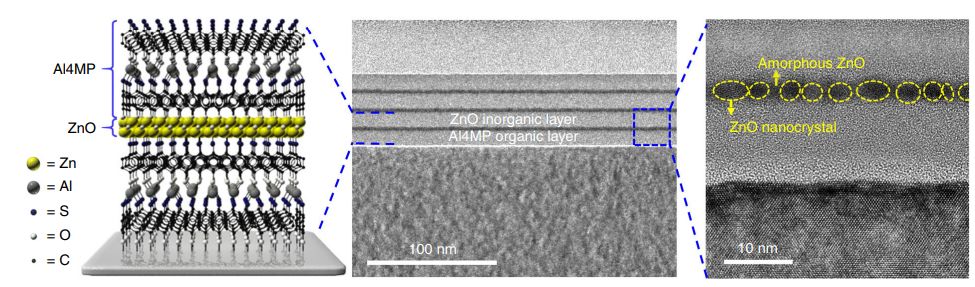

三进制逻辑计算所处理的信息为“0”、“1”和“2”,理论上三进制逻辑运算相较二进制逻辑运算可以实现单位面积减少37%的器件数量和36%互联线路。Kim教授研究团队的实现方法是在非晶态氧化锌复合纳米层中嵌入氧化锌量子点,并将复合纳米层与有机势垒层结合形成混合超晶格,研制出具有稳定中间态的多值逻辑晶体管。8 P* f$ n7 K. d/ h0 G( F

2 y; H8 W+ ?2 A) U# \+ Q. {8 J- |+ q% _% I _

图片来源:Nature communications, Kim团队论文

5 s7 w$ ]; f! n! ^: s( @6 {$ F

9 |" s" o" f, Z; [& E& M) `- n& B0 f% ?3 A1 `

) q! F' Y5 P" y1 O$ ?

9 V6 I9 U5 ]6 w* E# o

通过非晶态域选择性地与量子点共振杂化实现量化离散态杂化,在该局域态下,整个纳米层形成能级量化导电态。利用混合超晶格结构,以氧化锌复合纳米层和有机势垒壁为通道,在晶体管中实现了多进制逻辑晶体管。由于量子化导电状态的电流饱和,混合超晶格在晶体管中产生多个态。多进制晶体管表现出优异的性能特点、稳定可靠的运行、无电流波动,并且可根据超晶格通道中氧化锌复合纳米层的数目调节状态,例如二进制、三进制、四进制。, \1 }2 l7 q" X- R: ?

+ e |: ]- F3 U' @

* j, f4 d! w2 o1 f6 M6 s; }! @" Q不仅仅停留在纸面,三进制半导体商用可期

, r5 D. _+ J( r5 k

. h) J" [# B7 {$ A在Kim团队的研究中,主要通过分子层沉积(MLD)和原子层沉积(ALD)来分别制备带有铝连接体(Al4MP)的4-巯基苯酚(4MP)分子层和氧化锌纳米层,形成混合有机-无机超晶格薄膜。利用透射电子显微镜(TEM)对混合超晶格薄膜进行表征,证实了混合薄膜中单个Al4mp和ZnO纳米层达到了预期。

: o$ n5 @$ `# i7 O0 n- T' @& x

6 b m$ k8 }7 ~6 I图片来源:Nature communications, Kim团队论文 ) S6 Y- s; a3 _/ r, F" O) g

; r1 Q' W) I6 M6 c* P

# _/ {5 d# d3 m# R! N0 ]8 j在该制程中应用到的分子层沉积系统(MLD)通过将两种反应气体(或者蒸汽)以气体脉冲形式交替地引入反应器,依靠留在基底表面的吸附分子(如羟基或氨基)进行反应而生成薄膜,是一种高级的有机聚合物薄膜与有机无机杂化膜制备技术,主要适用于有机聚合物薄膜和有机无机杂化薄膜,可以实现每个循环沉积一个分子层,精确控制厚度,可以用于微电子、薄膜封装、生物芯片等诸多领域。: s: j9 R) d3 n# j

7 W0 w: _( R6 v* `- w' K

5 F! `8 z4 t3 d3 k8 M

原子层沉积(ALD)是一种可以将物质以单原子膜形式一层一层的镀在基底表面的方法,每次沉积只能沉积一层原子。沉积层具有极均匀的厚度,这一特点在微电子和深亚微米芯片技术的发展中显得极为重要。/ d3 r, ^- Z& _1 U* g

1 g) e" N# _. o

" k/ a, [- K5 ~# G5 ]$ [

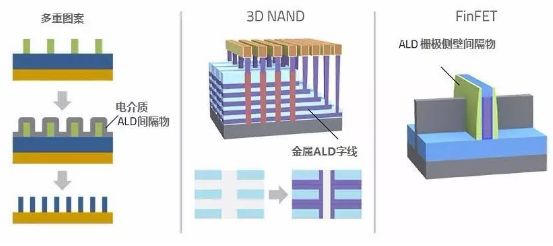

MLD和ALD都是在芯片制造过程中是常见的薄膜制备方法。在存储设备中,由于3D NAND存储器件的3D结构需要高度的工艺变异性控制,ALD非常合适用于在存储器孔的侧壁上形成介电膜。3 E" z! s4 K5 f

+ u$ r& x+ K% ?# k

; b' @7 ^1 X: O% x9 i8 L: [在FinFET中的薄栅极侧壁的间隔物必须形成极其均匀的厚度并没有小孔。ALD能把控制栅极和三维鳍结构分开,是沉积该层的绝佳方式。

$ d5 a2 I, w6 h; P( |9 {% I* m

5 h, O d% x8 @图片来源:雪球资讯 * W) L6 J; N; k* Q' V7 D- g

7 v9 [) L0 b6 i& u! }) d

$ a E3 Y! T9 `1 T# J: ^/ r8 v8 T当前摩尔定律逼近极限,行业者纷纷寻找下一代半导体发展方向之时,由三星支持的Kim教授团队取得的这一突破,无疑给半导体产业发展带来曙光,而对于三星来说意义也是非同寻常的,在二进制半导体时代,三星无疑是产业霸主,在未来的三进制半导体时代,三星也将持续引领产业走向。 + s, X6 C8 J3 M4 s4 S- h# }. A

/ o4 s6 r. Q) S5 t4 m4 J3 V

6 Y: V! v. n0 ~8 w

: t- i* D5 K6 p( ]2 @ A$ i \/ k. v: `' e2 x1 A$ ]8 U o

) i1 O- _: B: h

最新推荐阅读:* v2 n6 ]" d4 u- \) v

8 o+ r! [. D% N7 ]+ X- 三星承担所有额外费用,要求合作伙伴存储日本所有零部件90多天库存9 C' l+ T& y3 d8 F8 ?# k0 S3 x4 x

- 世界再无东芝存储器,公司正式改名"KIOXIA",中文名"铠侠",祝福KIOXIA新征程顺利 B6 s7 z+ j. O8 O

- 领先竞争对手,三星宣布量产业内首款12Gb LPDDR5,抢5G手机先机!

. @/ e4 m/ t$ \( k, ?8 h/ `4 G! m

+ W5 [3 J/ r L* K$ f% H# @4 g& F5 F, e. \

& @9 f; n0 Q' b, k3 A公司简介www.chinaflashmarket.com 中国闪存市场致力于为客户提供最新资讯、产品报价、数据汇集、产业分析、专题报道,以及最专业的存储产业咨询服务。2 x2 k6 C* W0 S1 Y1 [3 q

邮箱:Service@chinaflashmarket.com

) s# ~: g! \6 y: e# n9 D( K

# p, W% r8 |5 c& d: y3 h& L8 g7 t来源:http://mp.weixin.qq.com/s?src=11×tamp=1563598805&ver=1739&signature=qbnvOH9Qp2127BWtMfP7juU0IeV*UiVGUiz8lxj3umGRYqbFUJiC3qjBlD4fNQm*47pzoextZN4KWwRo5bUYSg7R0hIiOSpY*dG8vuScdxBevwpXf2A28diHNz0gth0Y&new=1

. G: ?1 J& i+ ?' r, d& f! J9 X6 M免责声明:如果侵犯了您的权益,请联系站长,我们会及时删除侵权内容,谢谢合作! |  /6

/6

|手机版|小黑屋|梦想之都-俊月星空

( 粤ICP备18056059号 )|网站地图

|手机版|小黑屋|梦想之都-俊月星空

( 粤ICP备18056059号 )|网站地图